The primary objectives of the DLX project were:

- Design and implement a functional DLX microprocessor using VHDL.

- To understand the principles of RISC architecture and pipeline processing.

- To validate the design through simulation.

- Synthesize the processor.

- Use a standard cell layout for Physical Design.

- Full automation for simulation, synthesis and physical design via scripts

DLX Features

Not the full instruction set has been implemented but only a subset, focusing on the fundamental operations required for basic computation:

- Arithmetic Instructions: R-type: ADD, SUB, SLL, SRL, SNE, SLE, SGE

- Arithmetic Instructions: I-type: ADDi, SUBi, SLLi, SRLi, SNEi, SLEi, SGEi

- Logical Instructions: R-Type: AND, OR, NOT, XOR

- Logical Instructions: I-Type: ANDi, ORi, NOTi, XORi

- Memory Instructions: R-Type: LOAD (LW), STORE (SW)

- Control Flow Instructions: JUMP, JAL, BNEZ, BEQZ

There have been implemented two features that enanches the DLX processor:

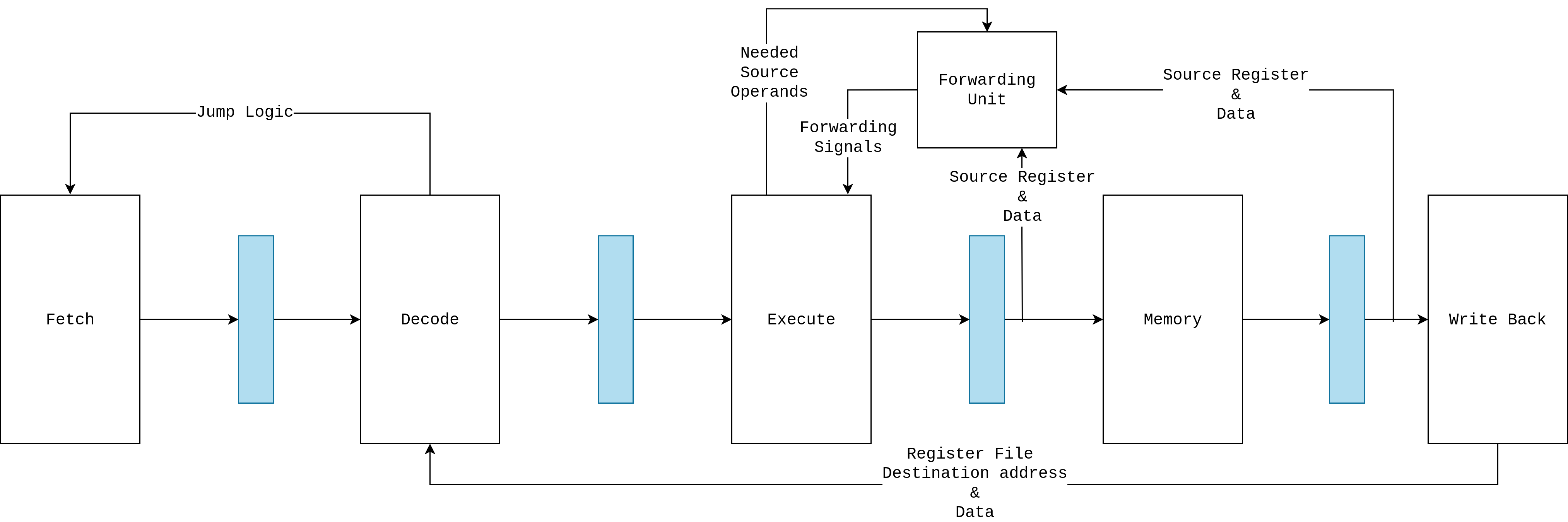

- Forwarding Unit: This unit is designed to handle data hazards by forwarding the results of previous instructions to subsequent instructions that require them, thus reducing the need for stalls in the pipeline.

- Branch Prediction: The DLX microprocessor incorporates a simple static branch prediction mechanism to improve the performance of control flow instructions. This feature helps to mini- mize pipeline stalls caused by branch instructions.

Implementation Structure

The DLX has been divided in a classical Control Unit and Datapath schema. The Datapath has been implemented via an Hardwired structure. Meanwhile the Datapath has been split in sub-components for each stage of the pipeline:

- Fetch

- Decode

- Execute

- Memory

- Write Back